英特尔刚刚嘲笑了即将推出的采用Xe架构的GPU,该GPU具有三种不同的包装。Raja Koduri嘲笑了三个Xe GPU,他参观了位于加利福尼亚州佛森市的Xe GPU实验室。

英特尔在BFP“超赞的包装”风格中戏弄了三个大型Xe GPU-即将进入您附近的数据中心!

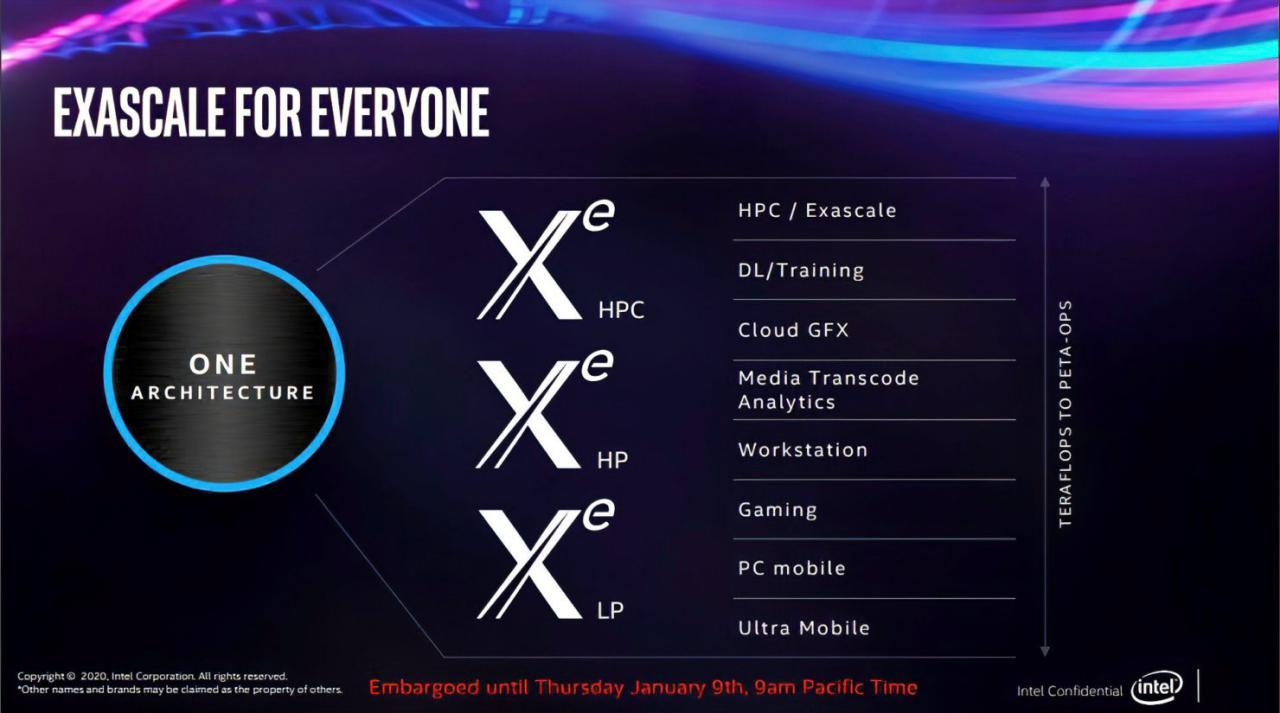

从Xe LP到Xe HPC,英特尔正在开发各种GPU,并将继续为其下一代图形产品组合提供动力。这些产品将由Xe HP和Xe HPC驱动的GPU掌控,这些GPU将在具有高达数百万亿亿次运算能力的计算机中使用。早在2019年12月Raja Koduri发布有关庆祝活动的消息时,英特尔就已经让我们瞥见了他们的Xe HP GPU之一,这标志着印度班加罗尔最大硅芯片开发的重要里程碑。

小姐的混乱和bringup labs..A一日游的美丽福尔瑟姆氙实验室pic.twitter.com/JKm90m5YB0

-Raja Koduri(@Rajaontheedge)2020年6月25日

Raja Koduri展示了运行预发布芯片的英特尔DG1 Xe-LP和Xe HPC GPU的测试板!

但是,即使是包装尺寸超过3500mm2的大型芯片,与Raja今天嘲笑我们的相比也算不了什么。首先,Raja推荐了三种不同的GPU软件包,其中包括我们之前看到的Xe HP软件包,以及一个较小的裸片和一个超大型的裸片,使其他两个芯片黯然失色。

根据我们的独家报告,以及英特尔就其Ponte Vecchio芯片所谈论的内容,英特尔似乎在MCM列车上全部使用,每个芯片都包含多个Xe GPU瓦片,这些瓦片将相互连接在一起,形成一个庞然大物。 GPU。以下是英特尔的各种基于MCM的Xe HP GPU的实际欧盟数量以及估计的核心数量和TFLOP:

Xe HP(12.5)1-Tile GPU:

512 EU [Est:4096核,假设1.5GHz,150W,则为12.2 TFLOPs]

Xe HP(12.5)2层GPU:

1024 EUs [Est:8192核,假设1.25 GHz时为20.48,TFLOP,300W]

Xe HP(12.5)4-Tile GPU:

2048个EU [Est:16,384核,36个TFLOP(假设1.1 GHz,400W / 500W)

在上面的两个镜头中,您可以看到配备Xe供电的DG1和Xe HPC GPU的实际测试板。您可以清楚地看到DG1 GPU被称为ES1,这意味着该单元来自早期的测试套件,并且还提到了12x8,等于96。基于Xe LP微型架构的DG1 GPU将具有96个EU,这可能是正在测试的旗舰款。在另一张图片中,您可以看到一个更有趣的部分,其内容为ATS-4T。这是上图中三个芯片中最大的,从外观上看,它是指该芯片内部代号为Arctic Sound,而4T可能是我上面提到的4块MCM设计。

Raja再一次安置了一块AA电池以进行规模化,我们肯定会在后续文章中提供更深入的文章,介绍其他两种芯片的具体封装尺寸。Raja Koduri还利用一种有趣的新术语来定义其Xe HP和Xe HPC零件的巨大尺寸,这些零件被称为BFP或Big Fabulous Package。第一个使用Xe HPC GPU的系统将是Aurora超级计算机,该超级计算机将于2021年部署,并将成为英特尔进入技术领域的领先7nm产品。

英特尔Xe GPU架构是为各种产品提供支持的一种可扩展架构。英特尔计划提供三种源自Xe的微体系结构。这些包括:

英特尔Xe LP(集成+入门/主流游戏)

英特尔Xe HP(发烧友,工作站/数据中心/人工智能)

英特尔Xe HPC(HPC Exascale)

虽然HPC将是第一个使用7nm Xe GPU的公司,但英特尔的10nm Xe GPU产品阵容将在2020年进入主流和发烧级游戏市场,这将利用消费者调整的Xe LP架构。英特尔最近向我们展示了其即将面世的Tiger Lake CPU中Xe LP GPU的首个演示,事实证明,这是英特尔集成显卡性能的重大飞跃。期望在未来几个月内获得有关Xe HP和Xe HPC GPU的更多信息。